Copyright © 2017 American Scientific Publishers All rights reserved Printed in the United States of America Journal of Nanoscience and Nanotechnology Vol. 17, 1622–1626, 2017 www.aspbs.com/jnn

# A Comparison of Power Factor in *N* and *P*-Type SiGe Nanowires for Thermoelectric Applications

Mohammad Noroozi<sup>1,\*</sup>, Bejan Hamawandi<sup>1</sup>, Ganesh Jayakumar<sup>2</sup>, Katayoun Zahmatkesh<sup>1</sup>, Henry H. Radamson<sup>2</sup>, and Muhammet S. Toprak<sup>1,\*</sup>

<sup>1</sup>Department of Materials and Nano Physics, SE16640 Kista-Stockholm, Sweden <sup>2</sup>Department of Devices and Circuits KTH Royal Institute of Technology, SE16640 Kista-Stockholm, Sweden

This work presents the thermoelectric properties of n- and p-type doped SiGe nanowires and shows the potential to generate electricity from heat difference over nanowires. The Si $_{0.74}$ Ge $_{0.26}$  layers were grown by reduced pressure chemical vapor deposition technique on silicon on insulator and were condensed to the final Si $_{0.53}$ Ge $_{0.47}$  layer with thickness of 52 nm. The nanowires were formed by using sidewall transfer lithography (STL) technique at a targeted width of 60 nm. A high volume of NWs is produced per wafer in a time efficient manner and with high quality using this technique. The results demonstrate high Seebeck coefficient in both n- and p-types SiGe nanowires. N-type SiGe nanowires show significantly higher Seebeck coefficient and power factor compared to p-type SiGe nanowires near room temperature. These results are promising and the devised STL technique may pave the way to apply a Si compatible process for manufacturing SiGe-based TE modules for industrial applications.

**Keywords:** Thermoelectric, SiGe Nanowires, Power Factor, Sidewall Transfer Lithography, Condensation.

# 1. INTRODUCTION

The efficiency of SiGe as a thermoelectric (TE) material has been improved and the reported data indicate a peak of conversion efficiency at high temperature interval of 900–950 °C.¹ This is a reason that SiGe alloys have inaugurated a platform for satellites in space for conversion of radio-isotopic heat to electricity or other high temperature power generation applications. The efficiency of TE materials, ZT is considered as the dimensionless figure-of-merit and is expressed as

$$Z \times T = \frac{\sigma \times S^2}{\tau} \times T \tag{1}$$

where S,  $\sigma$  and  $\tau$  are Seebeck coefficient, electrical conductivity and thermal conductivity, respectively. However, it is usually challenging to improve ZT because of strong interdependence of these transport coefficients. Recent developments on nanoscale materials have provided the possibility to further enhance the efficiency of

Even though enhancement of the TE figure of merit (ZT) through reduction of thermal conductivity is vastly investigated, a complete optimization to obtain higher power factor is still missing. It was shown that  $S^2 \times \sigma$  can be enhanced through quantum confinement and energy filtering effects. Hence a series of studies devoted a large effort to investigate the above concept on nanostructured TE materials. 9, 12–14

TE materials.<sup>2</sup> For example, nanowires (NWs) are one of the nanomaterial architectures which show capability to tailor the carrier transport and phonon conduction in a broad range of working temperatures.<sup>3–5</sup> This efficiency improvement is related to both reduction in thermal conductivity, because of surface and boundary scattering, and enhancement in power factor ( $S^2 \times \sigma$ ) due to manipulation of density of states around the Fermi level.<sup>3,6–9</sup> For example, 50% enhancement in ZT was observed in nanostructured p-type SiGe compared to bulk SiGe and a ZT of 0.46 was reported for SiGe NWs, more than twice compared to radioisotope TE generator (RTG) samples used by NASA space flight due to only reduction in thermal conductivity.<sup>10,11</sup>

<sup>\*</sup>Authors to whom correspondence should be addressed.

In this article, we report on the enhancement in power factor of both *n*- and *p*-type SiGe NWs with 60 nm width and 47% Ge content compared to previous reports so far.<sup>6,11</sup> This enhancement was attributed to electronic transport and structural quality of NWs. The NWs were processed through sidewall transfer lithography (STL) fabrication technique which is cost-effective and feasible for mass production. This paves the path to apply a Si compatible process for manufacturing TE modules for industrial applications.

# 2. EXPERIMENTAL DETAILS

A stack of  $\mathrm{Si_{0.74}Ge_{0.26}}$  (100 nm)/Si cap (10 nm) was epitaxially grown on Silicon on insulator (SOI) wafers with 50 nm Si top layer and 400 nm buried oxide. The wafers were loaded into the oxidation furnace for condensation of SiGe layer to higher Ge content. SiGe-on-insulator (SGOI) was manufactured by oxidation at 1050 °C for 90 min. The Ge content, layer thickness and the layer quality were determined by Rutherford back scattering technique (RBS) and high resolution X-ray rocking curves. <sup>15</sup>

The condensed SiGe layers were Boron (B) or Phosphorous (P)-doped by using diffusion method when  $B_2H_6$  or  $PH_3$  was flown over the substrate at 700°C for 10 min in chemical vapor deposition (CVD) reactor. Four-probe measurement was used to determine the sheet resistivity.

The doping concentration of n-type (P<sub>8</sub>doped) and n-type (B doped) SiGe NWs was estimated as  $7 \times 10^{16}$  generated TE potential over the NWs, the measurement and  $10^{17}$  cm<sup>-3</sup> from sheet resistivity of 0.0854 and n-was also performed by using the opposite heater. In this case, the values of voltage potential should be identical in SiGe compared to P has been previously reported. n-type (P<sub>8</sub>doped) and n-type (P<sub>8</sub>doped) and

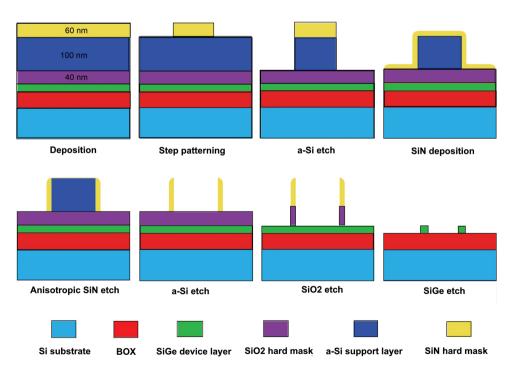

In this step, STL technique was used to form NWs on n- and p-type SiGeOI wafers. Figure 1 displays the schematic view of the STL process. The width of NWs is defined with nitride spacer thickness, which is controlled by deposition time and conformal deposition of the material. The good control over the process in STL depends on control over the thickness of deposited materials and good selectivity of wet and dry etching and highly directional etching during the process.  $^{18, 19}$

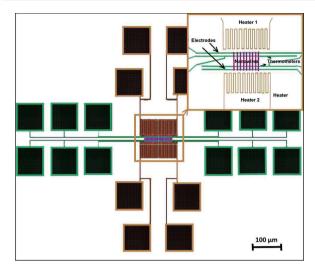

After the definition of NWs, metal electrodes thermometers and heaters were fabricated on both sides of NWs by evaporation of platinum (Pt) metal on patterned wafers. In order to assure ohmic contacts between nanowires and electrodes, 15 nm Nickel was deposited prior to the contact metallization followed by thermal annealing at 450 °C to form mono-crystalline of SiGeNi.<sup>20</sup> The temperature difference was obtained from the response of Pt thermometers resistivity when the heater is turned on applying DC current. The generated potential was measured using a Keithley 4200 SCS parameter analyser, which is used to calculate the Seebeck coefficient. The range of current and voltage measurement were 0.1 fA-1 A and 1  $\mu$ V-210 V, respectively. For these measurements, the estimated noise of current and voltage were in interval of 10-100 pA and  $10-20 \mu V$ , respectively. Two outer electrodes in the four probe configuration was used to measure electrical resistance of NWs, which is converted to electrical conductivity by using NWs dimensions. In order to confirm the generated TE potential over the NWs, the measurement case, the values of voltage potential should be identical in magnitude but with opposite sign. The final structure

Figure 1. STL process steps to fabricate SiGe NWs

**Figure 2.** A schematic view of TE structure, inner electrodes act as thermometers and outer ones as electrical electrodes. Pt heaters are located on both sides of NWs.

of TE component used to measure NWs TE properties is displayed in Figure 2.

## 3. RESULTS AND DISCUSSION

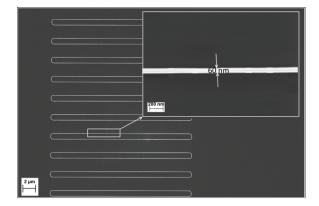

Fabrication of NWs with high crystalline quality and regular shape is not an easy task. Different types of damages may occur during the processing step, which causes the electrical properties to be degraded. Most of the work on TE NWs is based on fabrication via bottom-up techniques and transfer of a single NW onto a prefabricated device.<sup>5, 11</sup> This method is quite impractical in terms of integration with other components in a chip or for mass production for industrial application. In this respect, top-down techniques can be considered as a good solution for semiconductor device fabrication. Electron beam lithography (EBL), ion beam lithography (IBL), scanning probe lithography (SPL) and focus ion beam (FIB) are some techniques which are trying to go beyond the limits of the optical lithography resolution for sub-100 nm NWs fabrication. The problems with most of these techniques are being not cost effective and time consuming. STL is one of the techniques which seems quite practical to overcome these issues in NWs fabrication.21,22 The SEM image of formed NWs using STL technique is shown in Figure 3. The SiGe NWs fabricated with STL are continuous and exhibit the targeted width of 60 nm. A high volume of NWs is produced per wafer in a time efficient manner and with high quality using this technique.

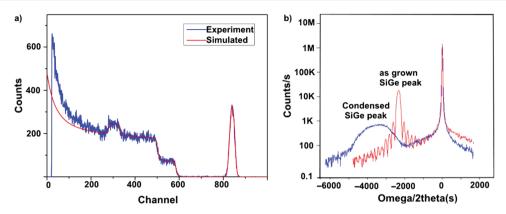

The Ge content and strain amount in the condensed SiGe layer are important issues since the electrical behavior of NWs depends on them. The mobility of SiGe is dependent on the bandgap and the strain amount and it increases with increasing Ge content.<sup>23, 24</sup> Figures 4(a and b) show the RBS result of condensed SiGe layer and rocking curves of SiGe layer before and

Figure 3. SEM image of SiGe NWs fabricated with STL technique.

after condensation. The simulated RBS result was used to estimate the Ge content as 47% and layer thickness of 52 nm, respectively. The broad shape of the condensed SiGe X-ray rocking curve with high full-width at half maximum (FWHM) value indicates a high defect density in the layer. The power factor, which is defined as  $S^2 \times \sigma$ , originates from electron density of states and electron effective mass.<sup>25</sup> In this case, the Seebeck coefficient becomes material dependent, and consequently the carrier mobility (or carrier scattering) will have a dominant effect as well. For TE materials a quite broad range of mobility and effective masses can be found. For example, SiGe with high mobility and low effective mass is well known as one of the excellent TE materials operational in high temperature application. The power factor in SiGe mostly can be improved by tuning conductivity through either doping or Ge content, but not through enhancement of Seebeck coefficient. In case of SiGe NWs when resistance of NWs increases dramatically with reduction of NWs dimension, the role of the Seebeck coefficient will be more important to manipulate the power factor.

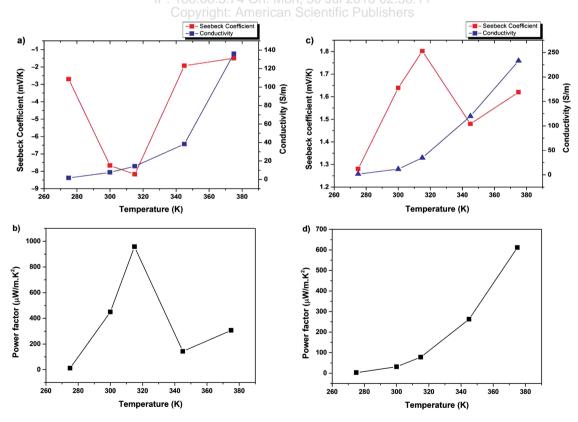

In this study, the Seebeck coefficient (as well as the power factor) of SiGe NWs is monitored by the dopant type. Figures 5(a and c) shows the Seebeck coefficient and electrical conductivity of lightly doped n-type and p-type SiGe NWs as a function of temperature. The value of the Seebeck coefficient generated by n-type SiGe has a maximum around 8 mV/K at 315 K, which even with low electrical conductivity obtained at this temperature can reach a power factor of 1000  $\mu$ W/mK<sup>2</sup>. This value is remarkably higher than the published data for SiGe NWs so far  $(700 \mu \text{W/mK}^2 \text{ for } \text{Si}_{0.63}\text{Geo}_{0.27})$ . This enhancement in power factor besides expectation for low thermal conductivity.<sup>11</sup> ensures high ZT for these types of n-type SiGe NWs. A Seebeck coefficient of 1.8 mV/K was observed for p-type SiGe NWs at similar temperature 315 K as shown in Figure 5(c). The high Seebeck coefficient can be obtained in lightly doped semiconductors when transport takes place away from Fermi level. Moreover the high Seebeck coefficient in both n and p-types SiGe NWs can be related to defects in layer, which were

Figure 4. (a) RBS spectrum of condensed SiGe layer and simulated one. (b) X-ray rocking curves of SiGe before and after the condensation.

created during condensation process. Both the experimental and theoretical work show that the significant enhancement of the Seebeck coefficient in semiconductors can be due to the sub-levels created within the bandgap which can act as potential barrier or energy filtering. 12, 13 The mechanism behind energy filtering is based on subtraction of carriers with higher and lower energy level with respect to the Fermi level. Therefore, high energy carriers contribute to the Seebeck coefficient resulting in significant improvement in electrical characteristics. 26 On the other hand, it is known that the interaction of defects is temperature dependent. This could be the reason for the

appearance of a peak for n-type and p-type SiGe samples at 315 K. Further investigations are necessary to figure out the type of defects that are involved for the changes in the Seebeck coefficient. The maximum power factor of n-type  $\mathrm{Si}_{0.53}\mathrm{Ge}_{0.47}$  NWs is about two times higher than p-type  $\mathrm{Si}_{0.53}\mathrm{Ge}_{0.47}$  ones, as shown in Figures 5(b and d) respectively. Although the same diffusion process has been applied, the resistivity data shows that the dopant level of B for p-doped SiGe layer is higher than n-type ones. Therefore, the carrier mobility in p-type SiGe NWs is lower than n-type, which can cause the Seebeck coefficient in p-type SiGe NWs to be lower than n-type NWs.

**Figure 5.** Thermoelectric parameters: Seebeck coefficient-electrical conductivity and power factor of (a, b) *n*-type, and (c, d) *p*-type SiGe NWs. The error margin for the measured data is less than 5%.

#### 4. CONCLUSIONS

Low dimensional TE structures based on *p*- and *n*-type SiGe NWs with cross-section of 60 nm × 52 nm were fabricated using STL technique. The STL method is a Si compatible process using one-step lithography when a nitride spacer is formed as hard mask to define NWs. The maximum Seebeck coefficients were 8 mV/K and 1.8 mV/K for *n*- and *p*-type SiGe NWs at temperature 315 K, respectively which reveal excellent power factor values for SiGe material. This behavior of the power factor is attributed to potential barriers originating from the defects during condensation of SiGe and formation of NWs. This study shows promising results for the implementation of SiGe NWs in future TE generators.

**Acknowledgments:** The authors acknowledge financial support from Swedish Foundation for Strategic Research "SSF" for this research (EM-011-0002).

### **References and Notes**

- X. W. Wang, H. Lee, Y. C. Lan, G. H. Zhu, G. Joshi, D. Z. Wang, J. Yang, A. J. Muto, M. Y. Tang, J. Klatsky, S. Song, M. S. Dresselhaus, G. Chen, and Z. F. Ren, *Appl. Phys. Lett.* 93, 193121 (2008)

- 2. L. D. Hicks and M. S. Dresselhaus, Phys. Rev. B 47, 16631 (1993).

- A. I. Boukai, Y. Bunimovich, J. Tahir-Kheli, J.-K. Yu, W. A. Goddard, and J. R. Heath, *Nature* 451, 168 (2008).

- M. Noroozi, B. Hamawandi, M. S. Toprak, and H. H. Radamson, ULIS 2014, Stockholm—15th Int. Conf. Ultim, Integr. Silicon, On. Stockholm, Sweden (2014), p. 125, DOI: 10.1109/ULIS.2014.

- M. Noroozi, A. Ergul, A. Abedin, M. Toprak, and H. H. Radamson, ECS Trans. 64, 167 (2014).

- 6. S. I. Yi and C. Yu, J. Appl. Phys. 117, 035105 (2015).

- 7. J. Chen, G. Zhang, and B. Li, Appl. Phys. Lett. 95, 073117 (2009).

- L. Shi, D. Yao, G. Zhang, and B. Li, Appl. Phys. Lett. 96, 173108 (2010).

- P. M. Wu, J. Gooth, X. Zianni, S. F. Svensson, J. G. Gluschke, K. A. Dick, C. Thelander, K. Nielsch, and H. Linke, *Nano Lett.* 13, 4080 (2013)

- 10. G. Joshi, H. Lee, Y. Lan, X. Wang, G. Zhu, D. Wang, R. W. Gould, D. C. Cuff, M. Y. Tang, M. S. Dresselhaus, G. Chen, and Z. Ren, Nano Lett. 8, 4670 (2008).

- E. K. Lee, L. Yin, Y. Lee, J. W. Lee, S. J. Lee, J. Lee, S. N. Cha,

D. Whang, G. S. Hwang, K. Hippalgaonkar, A. Majumdar, C. Yu,

B. L. Choi, J. M. Kim, and K. Kim, Nano Lett. 12, 2918 (2012).

- T. H. Zou, X. Y. Qin, D. Li, B. J. Ren, G. L. Sun, Y. C. Dou, Y. Y. Li, L. Li, J. Zhang, and H. X. Xin, J. Appl. Phys. 115, 053710 (2014).

- J.-H. Bahk, Z. Bian, and A. Shakouri, *Phys. Rev. B* 89, 075204 (2014).

- Y. Tian, M. R. Sakr, J. M. Kinder, D. Liang, M. J. MacDonald, R. L. J. Qiu, H. J. Gao, and X. P. A Gao, *Nano Lett.* 12, 6492 (2012).

- H. H. Radamson and J. Hållstedt, J. Phys. Condens. Matter 17, S2315 (2005).

- Y. Bogumilowicz, J. M. Hartmann, G. Rolland, and T. Billon, J. Cryst. Growth 274, 28 (2005).

- J. Hållstedt, A. Parent, M. Östling, and H. H. Radamson, *Mater. Sci. Semicond. Process.* 8, 97 (2005).

- J. Hållstedt, P. E. Hellström, and H. H. Radamson, *Thin Solid Films* 517, 117 (2008).

- G. Jayakumar, K. Garidis, P. Hellström, and M. Östling, *ULIS* 2014, Stockholm—15th Int. Conf. Ultim. Integr. Silicon, Stockholm, Sweden (2014), p. 109, DOI: 10.1109/ULIS.2014.6813928.

- X. X. Du, L. Sun, Y. Wang, L. Knoll, G. Mussler, B. Hollaeder, S. Mantl, and Q. Zhao, ICSICT 2012-2012 IEEE 11th Int. Conf. Solid-State Integr. Circuit Technol. Proc. (2012), p. 12, DOI:10.1109/ICSICT.2012.6467868.

- **21.** R. G. Hobbs, N. Petkov, and J. D. Holmes, *Chem. Mater.* 24, 1975 30 (**2012**).018 02:36:11

- LIS.2014 S 22 C. Ke and X. Chen, Silicon nanowires: Fabrication and application, elivered by In Anisotropic Nanomaterials Preparation, Properties, and Applications, adamson, edited by Q. Li (2015), pp. 1–25, DOI: 10.1007/978-3-319-18293-3.

- 23. D. Wang and H. Nakashima, Solid. State. Electron. 53, 841 (2009).

- 24. H. Y. H. Nakashima and D. Wang, ECS Trans. 25, 99 (2009).

- 25. A. Shakouri, Annu. Rev. Mater. Res. 41, 399 (2011).

- D. Narducci, E. Selezneva, G. Cerofolini, S. Frabboni, and G. Ottaviani, J. Solid State Chem. 193, 19 (2012).

Received: 14 March 2016. Accepted: 28 April 2016.